# Dedicated Simulation Platform for Signal Integrity

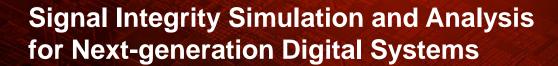

Xpeedic provides a fast, accurate and easy platform ChannelExpert to analyze, evaluate and solve high-speed channel signal integrity problems.

- 1. DDR bus analysis including transient, Stateye and PDA

- 2. SerDes channel analysis with IBIS-AMI models

- 3. Templated AMI model builder

- 4. Pre-layout channel analysis for IL\_fit, PSXT, ICN, COM and Eye-diagram

- 5. Support various analysis types: AC, DC, Transient, S-parameter, 2D RLCG solver, Stateye

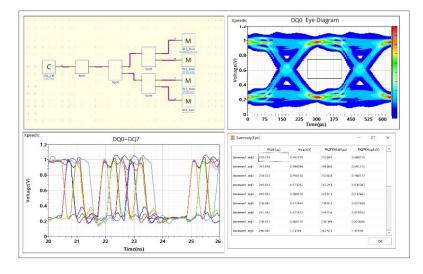

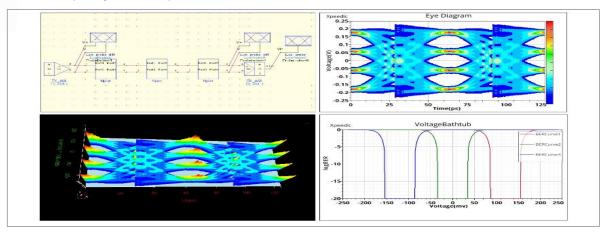

### **DDR Bus Simulation**

- The platform provides a fast schematic creation based on DDR buses.

- Support the transient, Stateye and PDA analysis with a user-friendly GUI and processing flow.

# **Highlights**

### 1

With the rapid development of artificial intelligence, cloud computing, big data, 5G and IoTs, the electronics industry is driven by the evolution of semiconductor technology.

### 2

The functionalities of electronic products are getting more diversified, which benefits from the faster signal speed and higher integration. The development cycle and go-to-market (GTM) time are also becoming short.

# 3

As electronic products continue to be miniaturized, sophisticated, and high-speed, the channel design needs to fully consider the entire interface link which consists of the transmitter, vias, transmission lines and receivers for accurate simulation.

# 4

Xpeedic provides a fast, accurate and easy platform ChannelExpert to analyze, evaluate and solve high-speed channel signal integrity problems, and has built-in industry-leading SPICE simulation engine, 2D transmission line solver and advanced analysis modules.

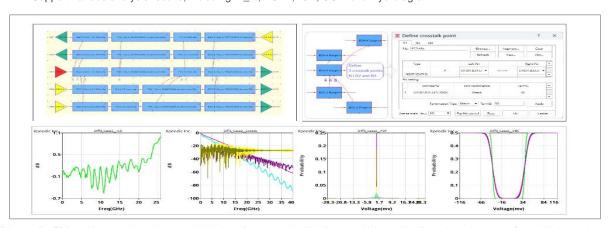

### **SerDes Channel Analysis**

- Support IBIS-AMI and built-in Tx/Rx buffers.

- Support statistical and bit-by-bit simulation modes.

- Provide Eye-diagram, BER, Eye contour, Bathtub and transient waveform results.

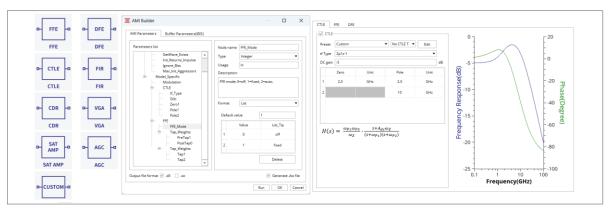

### **AMI Model Builder**

- Various SerDes blocks: FFE, DFE, CTLE, FIR, CDR and SAT AMP.

- Support pre-defined EQ parameter list for AMI models and one-click model generation.

- Built-in automated optimization of equalization parameters based on channel responses.

- Validation of the created models.

# Pre-layout Channel Analysis: IL\_fit, PSXT, ICN, COM and Eye-diagram

- Advanced channel creation based on S-parameter models of existing structures, such as vias, connectors, fan-out patterns.

- Flexible crosstalk interface creation by cascoding S-parameter models.

- Support various analysis results, including IL\_fit, PSXT, ICN, COM and Eye-diagram.