3DIC系统设计

背 景

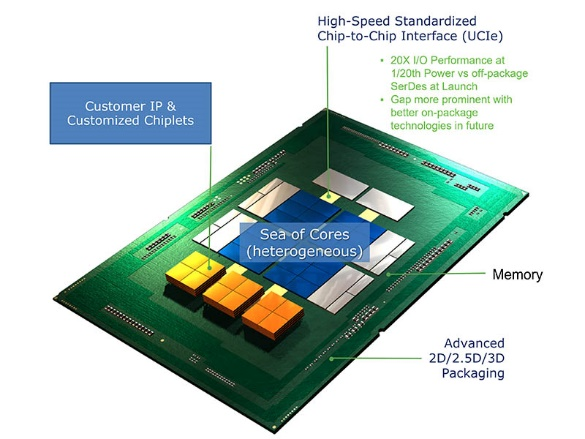

随着芯片制造工艺不断接近物理极限,芯片的布局设计——异构集成的 3DIC 先进封装(以下简称“3DIC”)已经成为延续摩尔定律的最佳途径之一。3DIC 将不同工艺制程、不同性质的芯片以三维堆叠的方式整合在一个封装体内,提供性能、功耗、面积和成本的优势,能够为 5G 移动、HPC、AI、汽车电子等领先应用提供更高水平的集成、更高性能的计算和更多的内存访问。然而,3DIC 作为一个新的领域,之前并没有成熟的设计分析解决方案,使用传统的脱节的点工具和流程对设计收敛会带来巨大的挑战,而对信号、电源完整性分析的需求也随着垂直堆叠的芯片设计流行而爆发式增长。

方 案

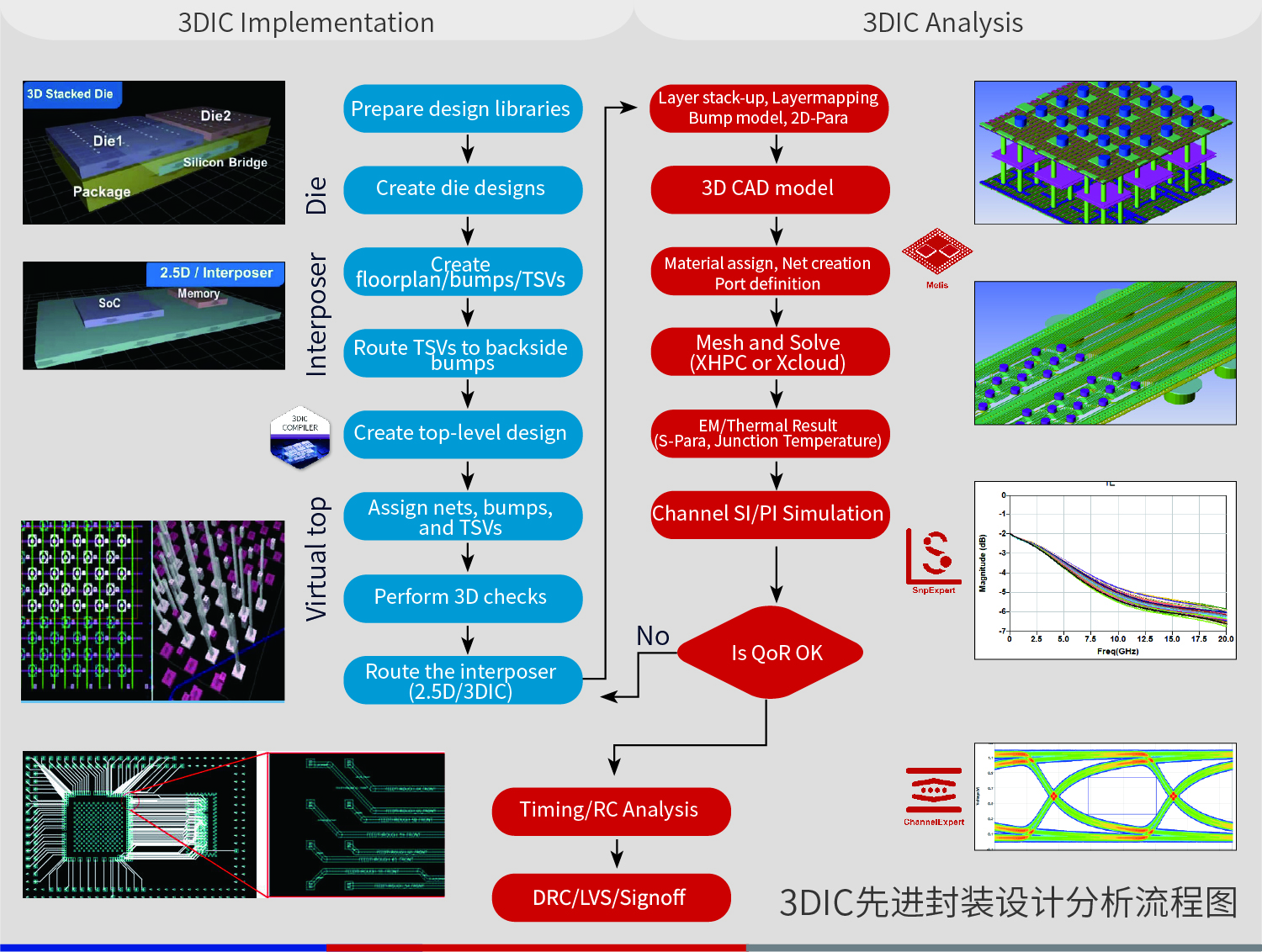

芯和半导体 3DIC 先进封装设计分析全流程 EDA 平台是一个由芯和半导体完全主导的平台,集合了 3DIC Compiler 面向 2.5D/3D 多裸晶芯片系统设计实现能力和芯和 Metis 在 2.5D/3D 先进封装领域的强大仿真分析能力 ,全面支持 TSMC 和 Samsung的先进封装工艺节点。

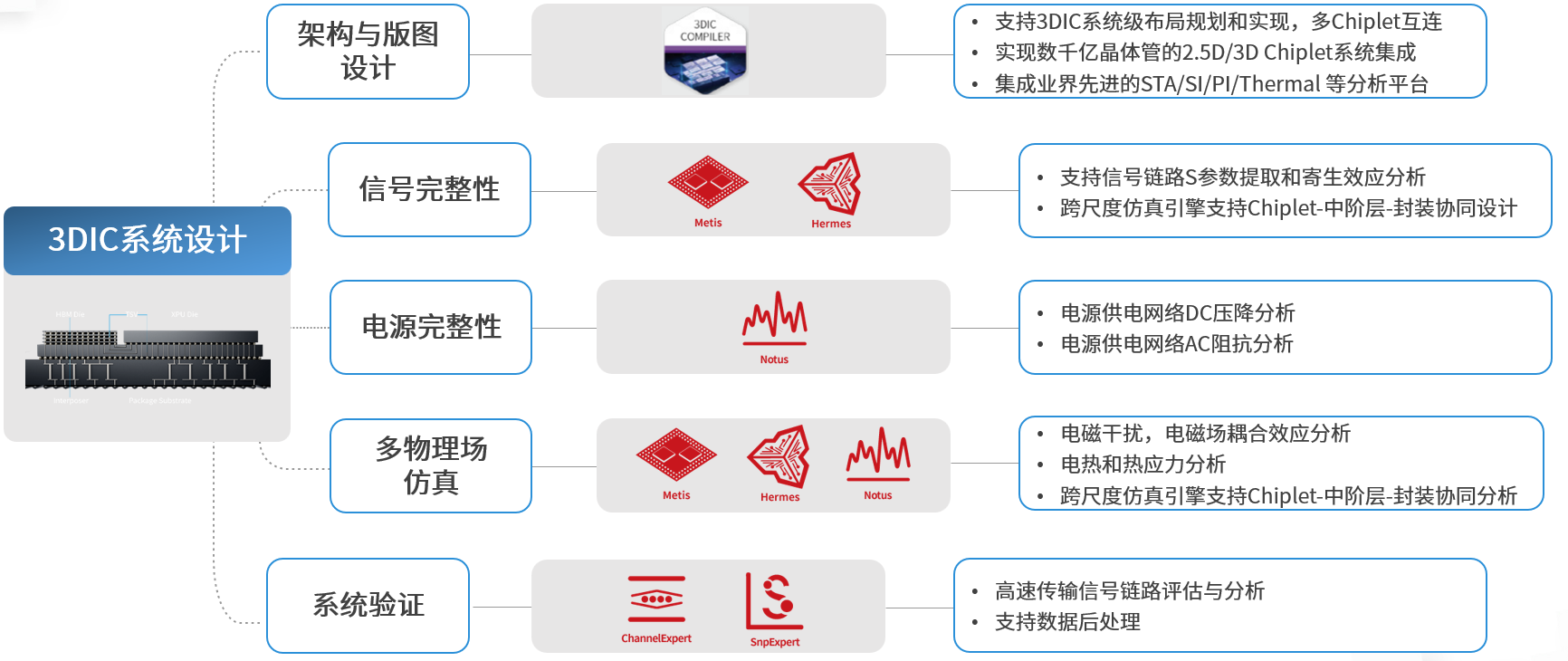

该平台提供了从架构探索、物理实现、分析验证、信号完整性仿真、电源完整性仿真到最终签核的 3DIC 全流程解决方案,是一个完全集成的单一操作环境, 极大地提高 3DIC 设计的迭代速度,并做到了全流程无盲区的设计分析自动化。通过首创“速度 -平衡 - 精度”三种仿真模式,帮助工程师在 3DIC 设计的每一个阶段,根据自己的应用场景选择最佳的模式,以实现仿真速度和精度的权衡,更快地收敛到最佳方案,芯和 3DIC 先进封装设计分析全流程 EDA 平台能同时支持芯片间几十万根数据通道的互连,具备了在芯片 -Interposer- 封装整个系统级别的协同仿真分析能力。

重要特色:

• 完全自主开发的仿真引擎

• 遥遥领先的跨尺度仿真能力

• AI 驱动的网格剖分技术

• 云计算加载的分布式并行计算能力

• 支持裸芯片、中介层和封装基板的联合仿真