Stress and Reliability

Background

In electronic components and chip packaging products, due to the different thermal expansion coefficients of various materials, the products are prone to warping and deformation during the packaging production and power-on process due to changes in different temperatures, resulting in problems of stress stretching and squeezing. As the semiconductor process continues to shrink, physical limits restrict further development of the process. The 2.5D/3D IC advanced packaging technology stacks 2D chips and connects them in the 3D direction, which is expected to further enhance chip integration density and significantly reduce interconnect latency and interconnect density. However, it also introduces many challenges. The reduction in wiring size increases the interference between interconnects, the reduction in chip spacing increases mutual interference, and heat generation will become a key bottleneck in constraining the system. It is necessary to reasonably plan and analyze the impact of heat and stress, avoid the risk of stress cracking caused by heat, and strengthen the high reliability of product design.

Solution

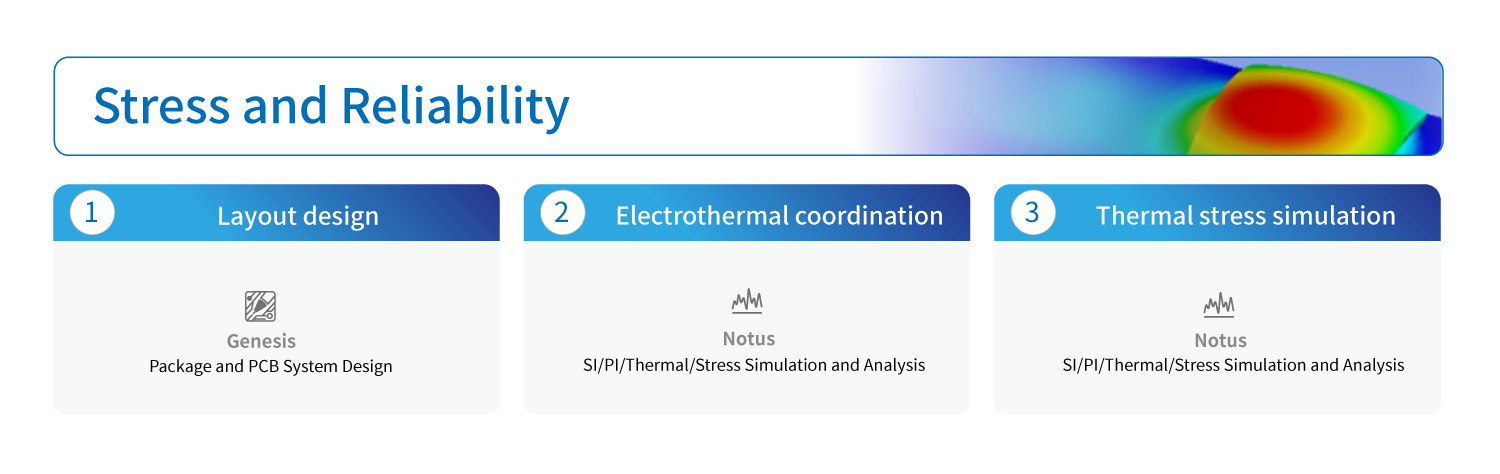

Xpeedic's Notus platform provides electrothermal and stress analysis process solutions, taking into account the effects of device heat and Joule heat, and accurately assessing temperature changes in the system. Based on thermal analysis, static analysis is completed under the stimulation of the temperature field, thereby obtaining the thermal stress analysis results of the model, effectively predicting and judging the stress reliability of the design.