IRIS——Accurate and fast EM simulation to enable RF and analog IC designs

Overview

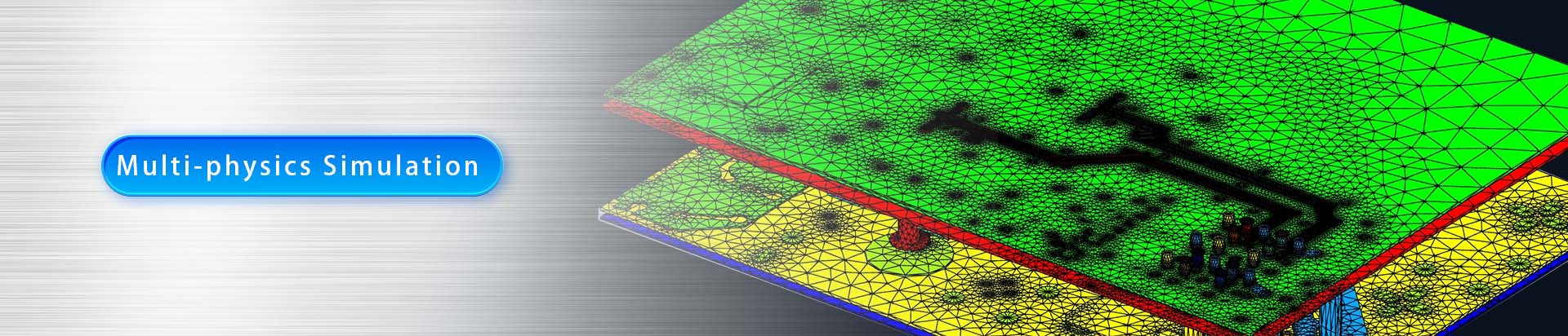

As the operating frequency increases, the extraction of parasitic parameters becomes particularly important. In the design of radio frequency and analog IC circuits, the interconnection and mutual coupling effects of passive devices and passive networks as well as the radio frequency passive must be considered through electromagnetic field ( EM ) simulation. Devices and multiple harmonic effects. The seamless integration of IRIS and Cadence Virtuoso not only enables designers to stay in the Virtuoso design environment to perform electromagnetic field simulations, but also achieves the perfect integration of the front-end and back-end of design verification through functions such as back-marking, synthesis, and optimization, which greatly helps IC designers reduce design cycle and achieve first-time silicon simulation success.

Key Features

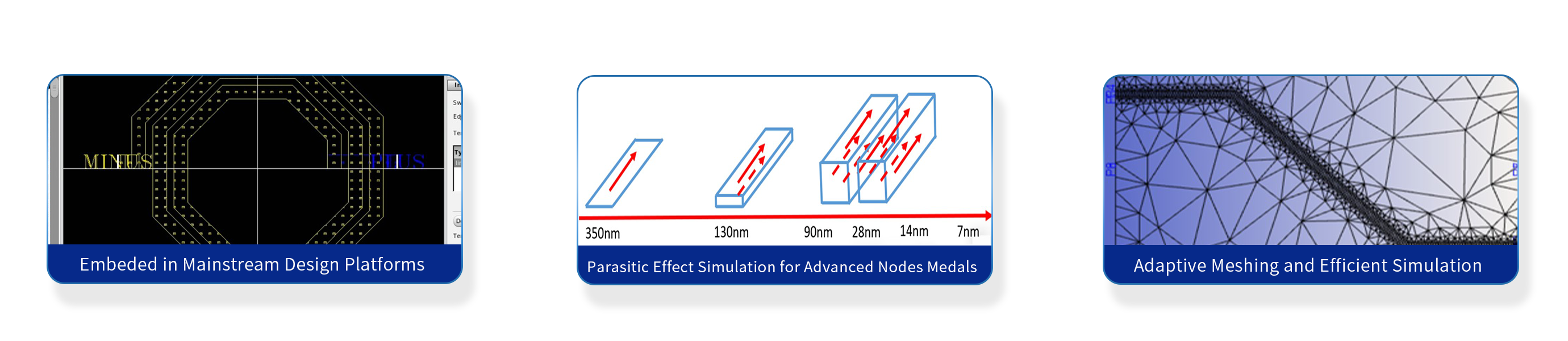

• Integration with the Cadence Virtuoso design platform allows designers to perform electromagnetic field simulations directly within the Cadence design environment. Including port type settings, scanning mode and frequency band settings, etc.

• The accelerated 3D planar EM solver based on the method of moments ( MoM ) provides the best performance in terms of speed and accuracy, correctly capturing the skin effect and proximity effect of advanced process node metals while taking into account the material properties of semiconductors.

• Optimize meshing to balance speed and accuracy, supporting mixed rectangular and triangular meshing to improve simulation speed and convergence.

• Bias table and rho table are defined in advanced node process files to take into account the effects of conductivity and actual metal line width as width and spacing change in the layout.

• Support parallel processing technologies, including multi-threaded processing and distributed processing, to improve the acceleration and efficiency of solver performance and make full use of hardware computing resources. At the same time, batch simulation is supported when there are multiple simulation jobs.