Events

Events

2024 Chiplet Summit

Time:Feb 6-8

Place:Santa Clara, CA

Overview

Chiplet Summit offers an insightful, leading-edge program for its first annual event! The participants will learn all about chiplet, including design, integration, packaging, test, and standards. You will also get insight into industry trends from panels and keynotes by major players and hot newcomers.

The Second Annual Chiplet Summit is the show chip designers can’t miss if they want to stay competitive. They’ll get the scoop on ways to make their chiplets run faster, scale better, use less power, and be more flexible.

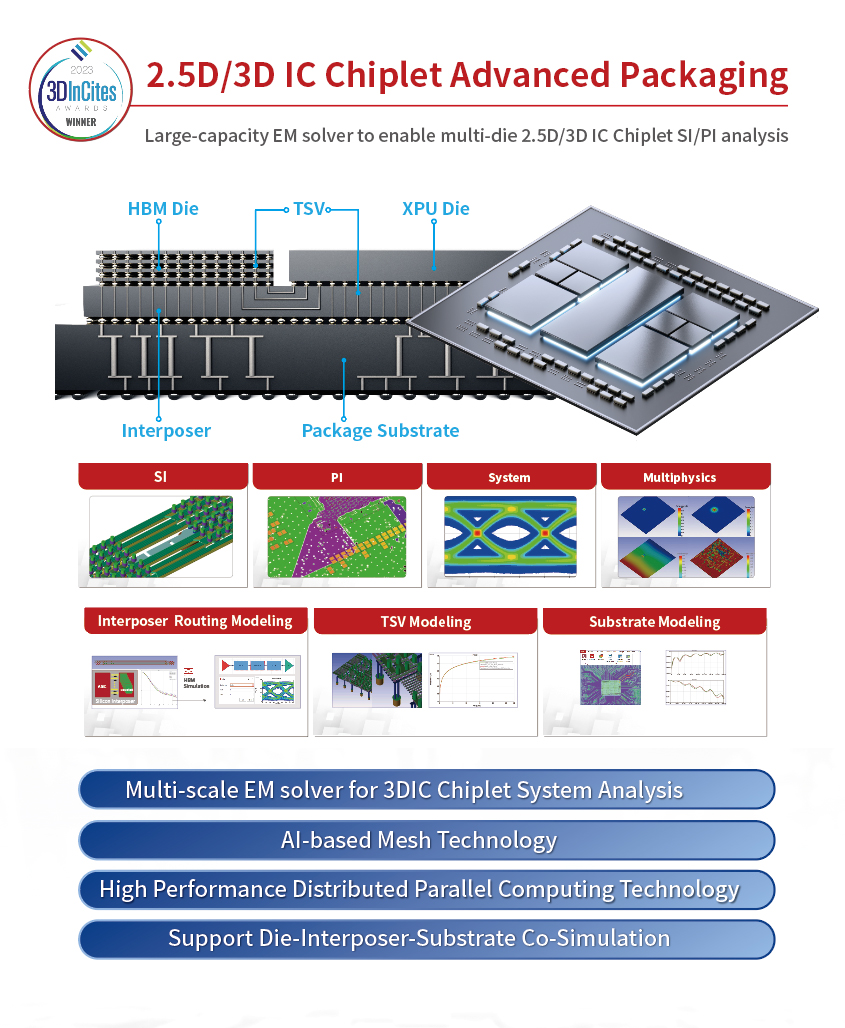

Xpeedic will release the latest updates for 2.5D/3D IC Chiplet Advanced Packaging at 2024 Chiplet Summit in San Clara, CA, Feb 06-08, 2024.

Booth Demo(#211)

Xpeedic will release the latest updates for 2.5D/3D IC Chiplet Advanced Packaging in the booth.

Dedicated electromagnetic simulation platform for 2.5D/3DIC Chiplet advanced packaging designs. This platform supports the pre-simulation and analysis for various interposer routings. It integrates interposer templates from the industry's mainstream 2.5D/3D packaging processes, which enables users to select the suitable routing types, set up dimension parameters and conduct a fast and accurate evaluation of the interposer routing. Metis can extract S-parameter and frequency-dependent RLCG parameter for signal links and power supply networks in the advanced package design. Due to the advanced algorithm-based solver and intelligent meshing technology, it allows large-capacity and high-frequency electromagnetic simulation for 2.5D/3D heterogeneous packages. Compared with the other tools in the industry, Metis has great advantages of higher speed and lower memory consumption for the simulation of advanced packaging structures.

Conference information at a Glance

Chiplets improve chip yields and costs, but still provide the performance of a large monolithic chip. Designers can mix-and-match chiplets, use the process technologies best suited to particular functions, take advantage of chiplet IP, simplify moves to new process nodes, and avoid wafer waste and manufacturing defects. Chiplets are the key to producing the extremely high-density, high-performance chips required for today’s networking, storage, AI/ML, analytics, media processing, HPC, and virtual reality applications.

Central Topics at Chiplet Summit:

Application Areas/Use Cases of Chiplets

Development Platforms for Chiplets

Optimization for Chiplets

Architectures for Chiplets

Packaging, Integration, and Test

Thought-Provoking Panels Where Attendees Can Ask Questions of Leading Experts:

Choosing the Right Architecture for Your Application

Next Great Breakthrough in Chiplets

Best Development Platform for Chiplets

Best Interface for Chiplets

What Standards for Chiplets Are Needed?

Optimizing Chiplets

2024

Feb 06-08