第一届集成芯片和芯粒大会

时间:2023年12月16-17日

地点:上海浦东嘉里大酒店

展位号:C1

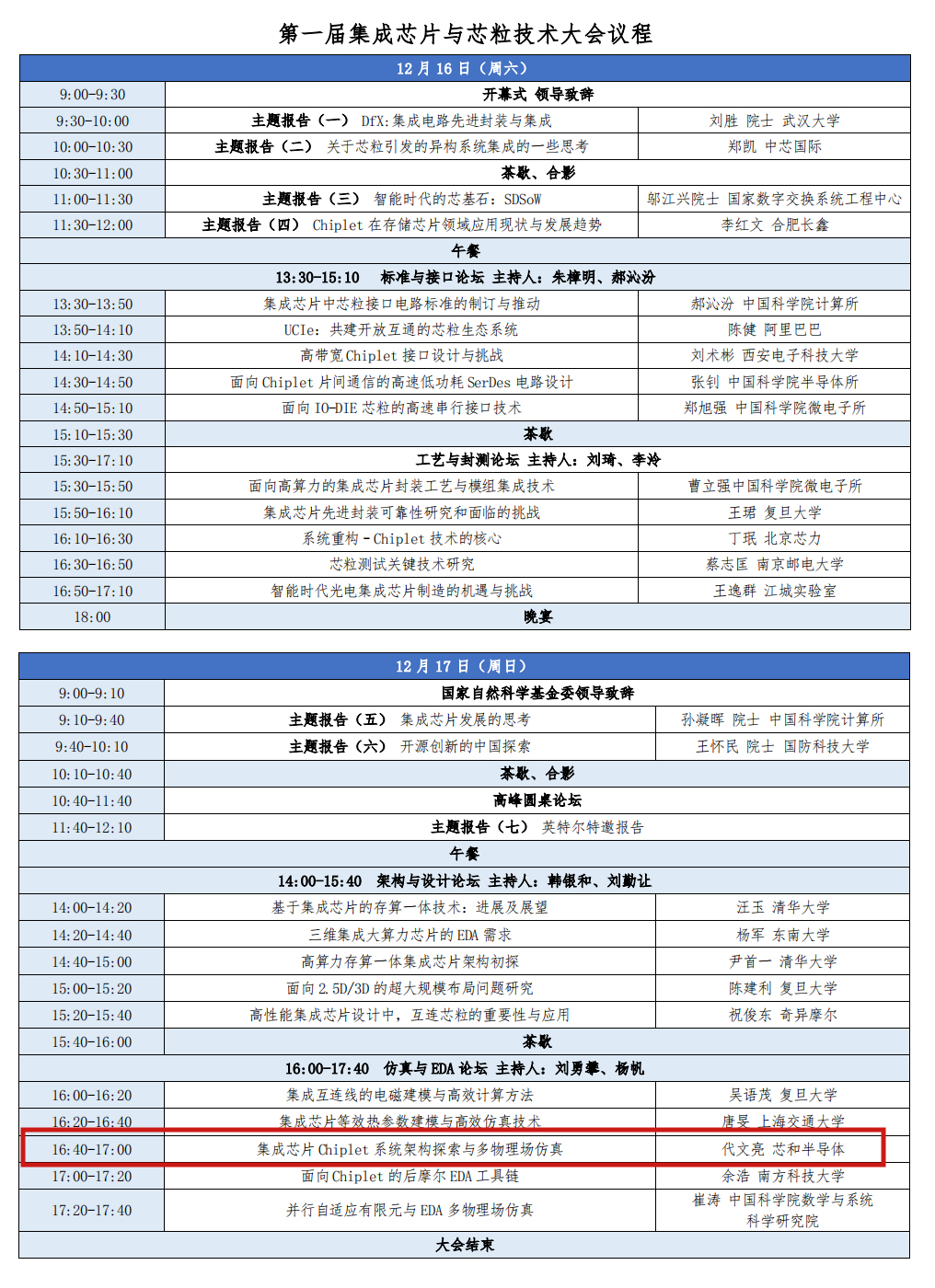

12月16-17日,芯和半导体将参加在上海浦东嘉里大酒店举办的“第一届集成芯片和芯粒大会”。芯和半导体联合创始人、高级副总裁代文亮博士将在17日下午的仿真与EDA论坛中发表题为《集成芯片Chiplet系统架构探索与多物理场仿真》的主题演讲。

除此以外,芯和半导体将在C1展台展示其2023旗舰产品——-3DIC Chiplet 一体化EDA设计平台以及完整的EDA应用解决方案和产品解决方案。

大 会 背 景

集成芯片(Integrated Chips)是通过半导体微纳工艺将若干芯粒再次集成的技术,以形成较单芯片更高集成度、更丰富功能的芯片和系统,是后摩尔时代集成电路的重要发展路径。2023年,在国家自然科学基金委员会的支持下,集成芯片前沿技术科学基础重大研究计划开始实施,聚焦在集成芯片中芯粒规模和种类大幅提升后的全新问题,并致力于发展出一条不完全依赖尺寸微缩的性能提升新路径。

首届集成芯片和芯粒大会(IC3: Integrated Chips and Chiplet Conference)以“跨学科探索集成芯片前沿技术”为主题,邀请该领域的专家学者,分享我国集成芯片研究与产业的最新进展,共同探讨集成芯片的未来发展趋势,引导对这一方向有兴趣的跨领域青年学者,共同开展集成芯片的科学基础和前沿技术的研究。大会研讨主题包括:1. 集成芯片的架构与设计;2. 集成芯片的标准与接口;3. 集成芯片的工艺与封装;4.集成芯片的仿真与EDA。

主 题 演 讲

演讲主题:集成芯片Chiplet系统架构探索与多物理场仿真

演讲人:芯和半导体联合创始人、高级副总裁代文亮博士

时间:12月17日 16:40-17:00

论坛:仿真与EDA论坛

摘要:随着摩尔定律的趋缓,先进工艺制程逐步逼近物理极限且经济效益越来越低,通过传统SoC(System on Chip)架构无法显著提升算力芯片性能、功耗和面积等指标,此时,基于先进封装技术的Chiplet成为突破瓶颈的重要技术之一,采用新型SoC(System of Chiplets)架构的芯片表现出明显优势,如更小的尺寸,更高的良率,不同工艺节点的Chiplet灵活复用大幅缩短上市时间,从而降低成本。本次演讲将深入浅出地分享Chiplet技术的特色,从架构和顶层设计方面探索高性能算力芯片的实现路径与关键技术,以及如何构建EDA解决方案应对Chiplet的多物理场仿真挑战。

展 台 演 示

会 议 议 程

2023

12月16-17日